現貨庫存,2小時發貨,提供寄樣和解決方案

熱搜關鍵詞:

在工業自動化、醫療電子及精密測量系統中,高性能模數轉換器(ADC)常需要通過電氣隔離來保障安全性或消除接地環路干擾。然而,隔離技術若處理不當,可能嚴重影響ADC的精度和動態性能。本文將重點分析隔離式高性能ADC設計中的三大關鍵要素:時鐘隔離、電源隔離與數據隔離,并提供具體的設計建議。

高性能SAR ADC(如LTC2378-20)或Σ-Δ ADC(如AD7760)對時鐘抖動極為敏感。以LTC2378-20為例,其孔徑抖動為4 ps RMS,在1 MSPS采樣率下可實現超過100 dB的信噪比(SNR)。一旦引入較大的時鐘抖動,系統性能將急劇下降。

標準數字隔離器(如ADuM系列)通常引入70 ps RMS以上的抖動,僅適用于低頻應用。

優化型時鐘隔離器(如LTM2893)可將抖動降低至30 ps RMS,支持50 kHz輸入頻率下的高SNR。

LVDS時鐘隔離器(如ADN4654)具備超低抖動(約2.6 ps),接近ADC本征性能極限。

時鐘凈化方案可通過PLL(如ADF4360-9)進一步降低抖動,再結合觸發器進行分頻,確保滿足LTC2378等高速ADC的時鐘要求。

此外,也可考慮在隔離側本地生成時鐘,但需注意異步時鐘域帶來的同步問題。

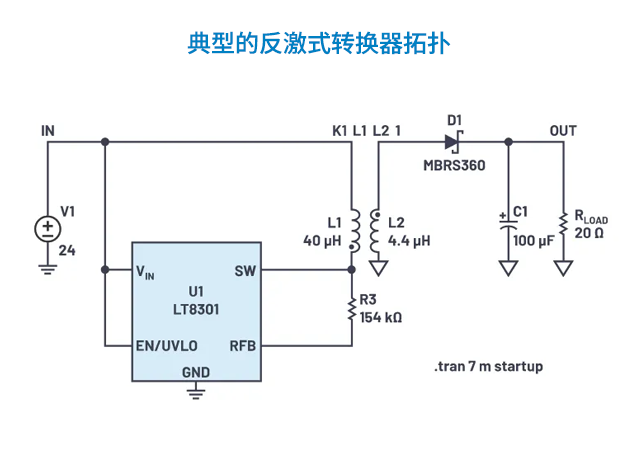

隔離電源是影響ADC精度的重要因素之一。傳統反激拓撲結構雖然簡單,但存在以下問題:

開關瞬變大,造成EMI輻射;

磁性元件利用率低,變壓器體積大;

輸出電壓紋波較高,需額外濾波;

負載變化導致開關頻率漂移,增加噪聲不確定性。

相較之下,推挽式拓撲(如LT3999)具有更低的EMI特性,并支持外部時鐘同步。通過與ADC采樣時鐘同步,可在采樣階段前預留“安靜窗口”,顯著降低電源噪聲對信號采集的影響。例如,LTC2378-20的采樣時間為312 ns,配合LT3999可輕松匹配<1 μs的無噪聲窗口。

數據隔離一般采用數字隔離器(如ADuM140x)實現,適用于SPI、I2C等接口。盡管其對系統整體性能影響較小,但仍需注意:

確保足夠的隔離耐壓等級;

使用重疊PCB平面或外接電容提供電流返回路徑;

隔離后端應盡量減少數字噪聲反饋至模擬前端。

對于SPI接口,只需隔離SCLK、SDO、CS等信號線即可實現完整的數據通道隔離。

設計一個高性能隔離ADC系統,需從時鐘、電源和數據三個維度綜合考量:

優先保證時鐘穩定性與低抖動,避免使用普通隔離器直接驅動ADC時鐘;

選擇推挽式而非反激式隔離電源,以獲得更清潔的供電環境;

合理使用數據隔離器件,并注意PCB布局以抑制共模噪聲。

通過上述方法,工程師可以在復雜工況下實現高于100 dB SNR的高精度信號采集系統,滿足高端工業、測試儀器和醫療設備的需求。